Na każdego przyjdzie pora

Pisałem już o trybie rzeczywistym. Przyszła więc pora napisać o trybie chronionym (ang. protected mode, nazywany też w skrócie pmode) i o powiązanym quasi-trybie Virtual 8086. Nie muszę chyba kolejny raz wspominać, iż tryb chroniony jest najważniejszym i najpowszechniejszym trybem architektury x86. Warto zatem wiedzieć, co tak naprawdę nam oferuje.

Historia

Tryb chroniony został wprowadzony w 1982 roku wraz z procesorem Intel 80286. Niestety nie został on przyjęty zbyt ciepło, głównie z powodu braku wsparcia aplikacji napisanych dla trybu rzeczywistego. Większość programistów postanowiła pozostać więc w trybie rzeczywistym, dostępnym bezpośrednio po uruchomieniu jednostki 80286 i nie włączać trybu chronionego. Architekci Intela wyciągnęli wnioski z tego zdarzenia i sytuacja uległa zmianie w 1985, gdy na rynek wszedł procesor Intel 80386, wnoszący wiele udogodnień, w tym możliwość powrotu z trybu chronionego do trybu rzeczywistego. Od tej pory tryb chroniony króluje we wszystkich systemach operacyjnych na platformę x86.

Ochrona

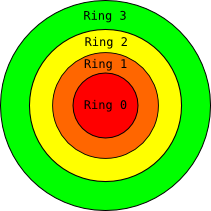

Nazwa trybu chronionego wzięła się z faktu, iż służy on szeroko rozumianej ochronie :). O ogólnym zarysie zdarzyło mi się już pisać. Każdy z mechanizmów opisanych poniżej podlega owej ochronie i jest to absolutnie pozytywna cecha. Zdecydowanie najważniejszą cechą trybu chronionego jest to, że pozwala on pisać bezpieczne systemy operacyjne – takie, w których można dokładnie zdefiniować prawa dostępu dla użytkownika, poza które nie może wykraczać. Można zadać pytanie – z jakiego powodu systemy operacyjne posiadają wciąż tyle błędów, skoro udostępnione mechanizmy są poprawne? Odpowiedź na to pytanie jest prosta – są to błędy programistów, którzy owych mechanizmów korzystają w sposób niepoprawny. Tryb chroniony jest dopracowanym i przemyślanym przez lata mechanizmem sprzętowym – wykorzystuj go dobrze! :)

Dostępne mechanizmy

To co możliwe jest w trybie rzeczywistym wyszczególniłem w swoim artykule. Wszystko pozostałe dostępne jest wyłącznie z poziomu trybu chronionego. Mechanizmy, o których zdecydowanie warto pamiętać to:

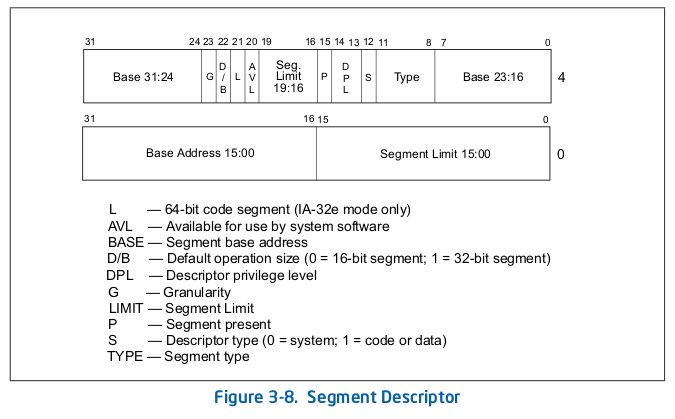

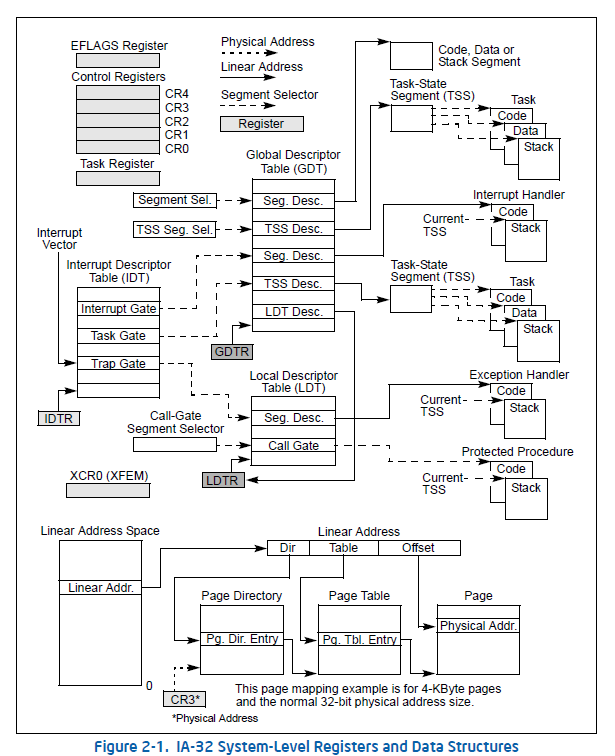

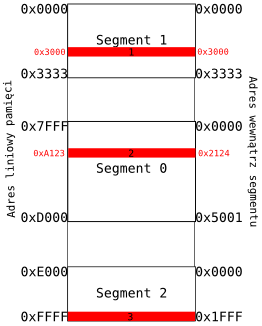

- Segmentacja

- Stronicowanie

- Możliwość powrotu do trybu rzeczywistego oraz tryb V8086

- Fizyczna i wirtualna 4 gigowa przestrzeń adresowa – jeśli posiadamy 4GiB RAM-u – możemy korzystać z niego do woli! Jeśli posiadamy trochę mniej, możemy zbudować pewien poziom abstrakcji „udający” owe 4GiB i to per proces!

- Wielozadaniowość (z wywłaszczaniem) – możliwość współbieżnego uruchamiania aplikacji, wspierana sprzętowo, możliwa do realizacji programowo.

- Rozbudowana obsługa wszelakich wyjątków – poprzez IDT możliwa jest obsługa wszystkich rodzjaów wyjątków: przerwań, błędów oraz pułapek.

- Możliwość korzystania z dobrodziejstw takich jak: wieloprocesorowość, kontrola cache’u, kontrola stanu procesora, w tym zarządzanie energią czy debuggowanie, dostęp do jednostek specjalnych takich jak MMX czy SSE, wydajny dostęp do sprzętu.

- I sporo innych ;).

To czego natomiast nie mamy, to dostęp do przerwań BIOS-u. Cały sprzęt musimy oprogramować sami.

Virtual 8086

Quasi-tryb V8086, to już raczej przeszłość. Umożliwia on uruchamianie aplikacji 16 bitowych w trybie zgodności i co istotne, działają one współbieżne z innymi aplikacjami. Niestety zgodność nie jest stuprocentowa – programy uruchomione w V8086 nie mogą korzystać z instrukcji systemowych, nie mogą manipulować segmentami, używać bezpośrednio sprzętu i uruchamiać kodu samomodyfikującego się. To, do czego może się przydać V8086 to wywoływanie funkcji BIOS-u, np. zmiana trybu graficznego. Używając tego trybu należy jednak uważać – ma on dostęp do pierwszego MiB pamięci, gdzie często znajduje się kernel (a nie powinien).

Gdzie i jak?

Wejście do trybu chronionego jest proste i wymaga ustawienia odpowiedniego bitu w rejestrze CR0 – dokładniej opiszę to w następnym poście. Wyjście natomiast, nie jest już takie proste. Można o tym przeczytać tu.

Z Virtual 8086 jest jeszcze trudniej, całościowe ujęcie tematu tutaj.

3..2..1..START!

Teraz wiemy już wszystko co potrzebne nam do przejścia i oprogramowania trybu chronionego. A więc do dzieła! Wszystko to w najbliższym odcinku!